Представлена технологія для енергоефективних 2-нм чіпів за авторством IBM та Rapidus

Arkadiy Andrienko

Arkadiy Andrienko

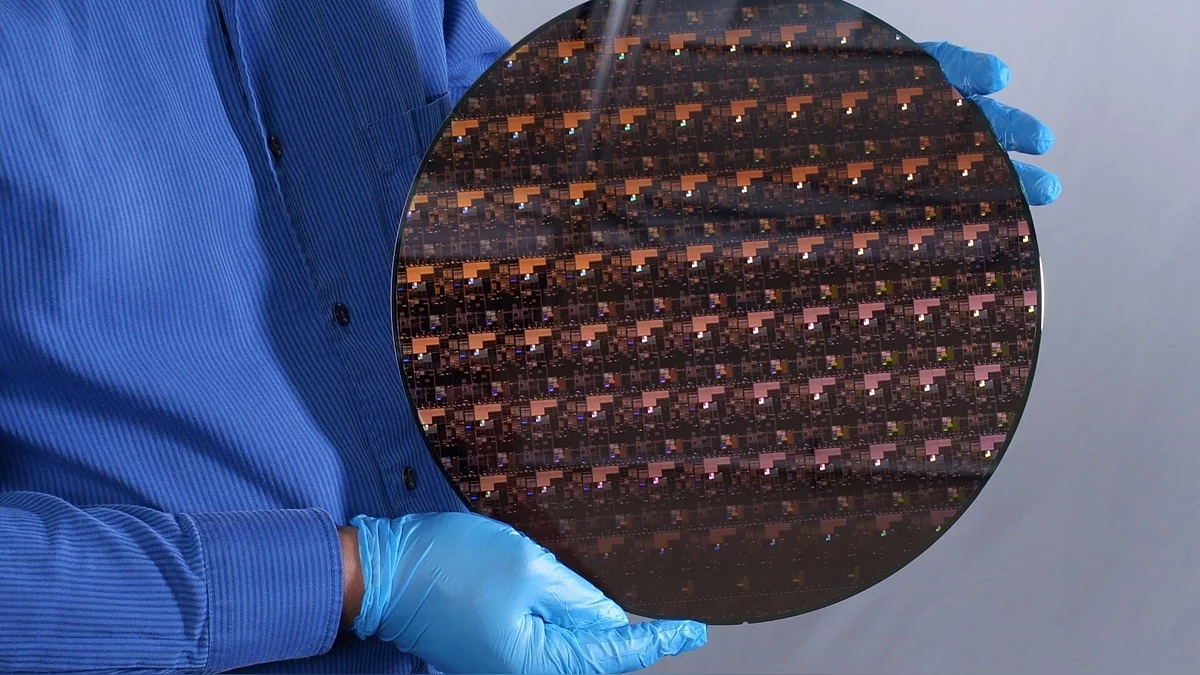

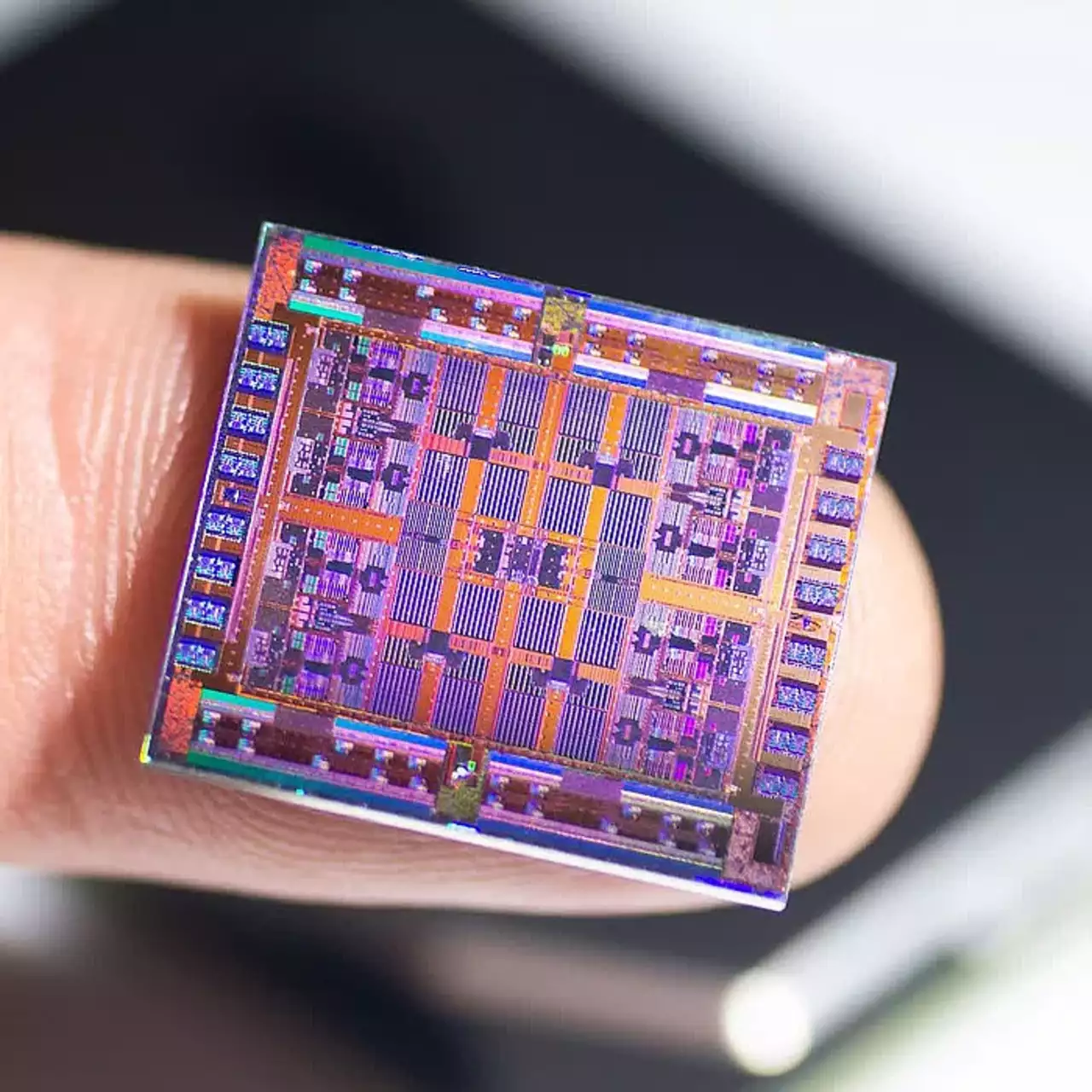

На конференції IEDM 2024 компанії IBM та Rapidus представили важливе досягнення в галузі напівпровідників. Партнери анонсували успішний поступ до масового виробництва 2-нм чипів, розробивши методи для випуску як високопродуктивних, так і енергоефективних модифікацій цих чипів. Очікується, що до кінця десятиліття ці технології будуть реалізовані на заводі компанії Rapidus в Японії.

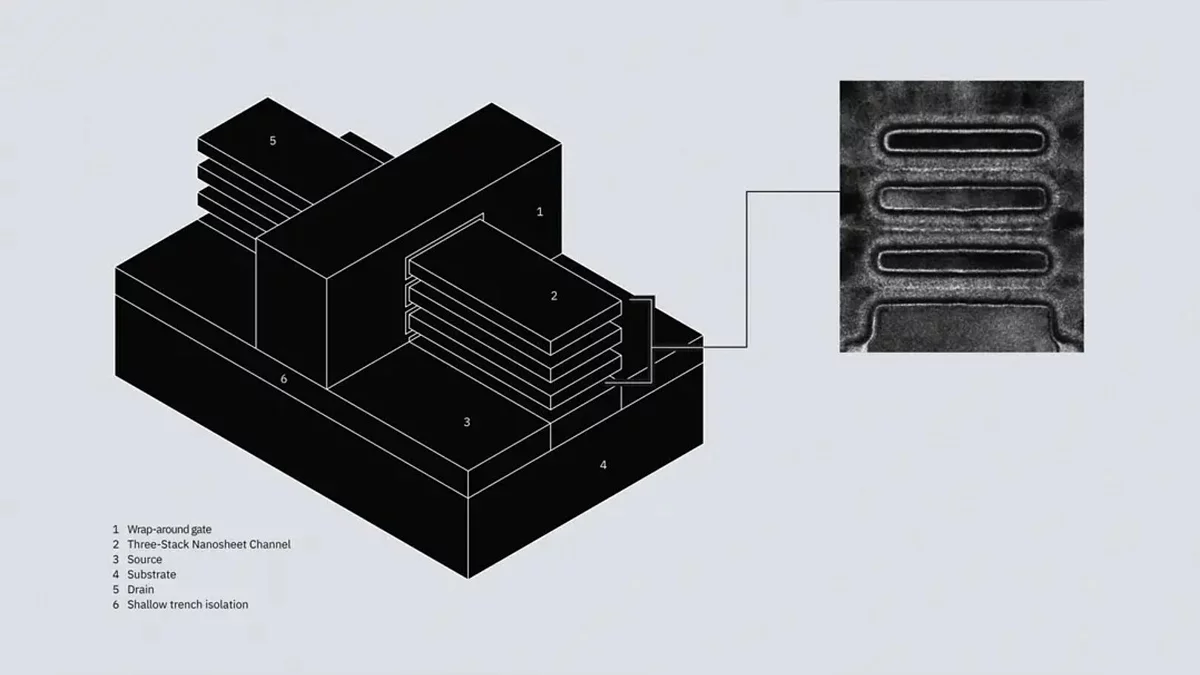

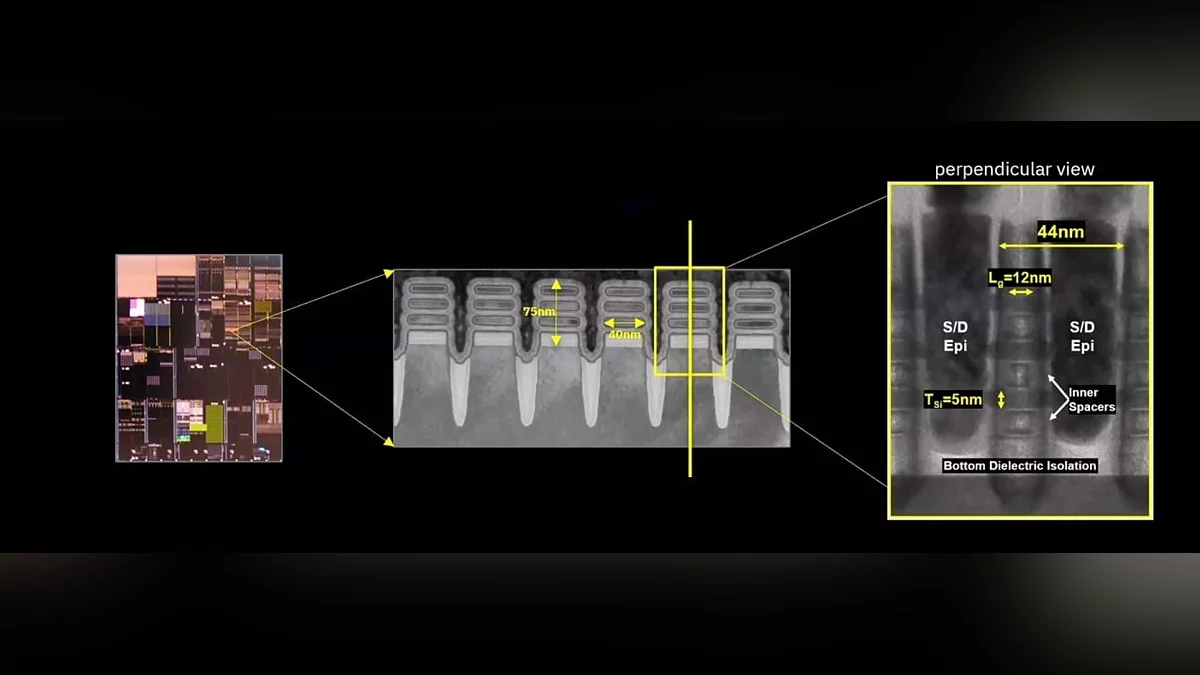

В ході конференції були представлені інноваційні методи виробництва, включаючи використання GAA-транзисторів з кількома пороговими напругами для різних типів пристроїв. Це дозволяє створювати чипи з високою продуктивністю для потужних систем і з низьким енергоспоживанням для мобільних або енергоефективних рішень. Особливу увагу було приділено технології вибіркового зменшення шару (Selective layer reductions, SLR), яка дозволяє точно контролювати порогове напруження в залежності від товщини проміжку між напівпровідниковими каналами.

Важливим досягненням стало також зниження забруднення підкладки чипів іонами в процесі травлення, що підвищило чистоту виробництва і дозволило зменшити дефекти в кінцевих продуктах. Генеральний менеджер Rapidus US зазначив, що впровадження мультипорогових напруг (Multi-Vt) в архітектуру чипів стало ключовим етапом розвитку компанії і впевнено просуває її до реалізації амбітних цілей зі створення передового напівпровідникового заводу на Хоккайдо.

З розвитком технологій виробництва 2-нм чипів, майбутні процесори зможуть запропонувати як рекордну продуктивність, так і енергоефективність, що відкриє нові горизонти для мобільних пристроїв, комп'ютерів та інших технологій.

-

![]() Ліза Су передбачає зміну GPU на ІІ-чіпи протягом п'яти років

Ліза Су передбачає зміну GPU на ІІ-чіпи протягом п'яти років -

![]() Intel і AMD об'єднуються для спільної роботи над x86-чіпами

Intel і AMD об'єднуються для спільної роботи над x86-чіпами -

![]() Maxwell Labs обіцяє революцію в охолодженні чіпів

Maxwell Labs обіцяє революцію в охолодженні чіпів -

![]() AMD запатентувала новий метод укладання чиплетів для збільшення продуктивності

AMD запатентувала новий метод укладання чиплетів для збільшення продуктивності -

![]() Neuralink тестує керування роборукою через мозковий чип

Neuralink тестує керування роборукою через мозковий чип